校园招聘FPGA工程师是高校学生进入半导体、通信、人工智能等高科技行业的重要途径,随着数字化转型加速,FPGA技术在硬件加速、实时数据处理等领域的需求持续增长,企业对FPGA工程师的招聘门槛与能力要求也逐步提升,以下从岗位认知、能力要求、求职准备、面试流程及职业发展等方面展开详细分析。

岗位认知与行业趋势

FPGA(Field-Programmable Gate Array,现场可编程门阵列)工程师是从事FPGA芯片设计、开发、验证与优化的专业技术人员,核心职责包括根据需求设计逻辑电路、编写硬件描述语言(HDL)代码、进行功能仿真与时序分析、配合团队完成系统集成与调试等,当前,FPGA技术广泛应用于5G通信基站、数据中心加速卡、自动驾驶、工业控制、人工智能计算等领域,尤其在需要高并行度、低延迟处理的场景中不可替代。

从行业趋势看,随着摩尔定律逼近物理极限,异构计算成为主流,FPGA与CPU、GPU的协同设计需求激增;国内FPGA产业正处于国产化替代的关键期,头部企业如紫光同创、高云半导体等加速布局,推动市场对本土FPGA工程师的需求攀升,据行业调研数据显示,2025年国内FPGA相关岗位招聘量同比增长35%,应届生起薪较传统电子类岗位高出20%-30%,具备实战经验的复合型人才更是供不应求。

核心能力要求

企业招聘FPGA工程师时,通常关注候选人的“理论基础+实践技能+项目经验”三维能力,具体可细分为以下几类:

专业基础知识

- 数字电路与逻辑设计:掌握组合逻辑电路(如译码器、 multiplexer)、时序逻辑电路(如触发器、计数器)的设计原理,熟悉状态机(Moore/Mealy机)的设计方法。

- 计算机体系结构:理解流水线、存储器层次结构(Cache、SRAM、DRAM)、总线协议(AXI、PCIe)等,能进行硬件架构的初步规划。

- 半导体工艺与器件:了解FPGA的基本结构(LUT、BRAM、DSP、PLL)、配置原理及不同厂商(Xilinx/Intel/国产)器件特性差异。

工具与技能掌握

- 硬件描述语言:熟练掌握Verilog或VHDL,能编写规范、可综合的代码,熟悉Testbench搭建与仿真验证流程。

- 开发工具链:掌握Xilinx Vivado/Vitis、Intel Quartus Prime等主流开发环境,能完成代码综合、实现(布局布线)、时序分析及生成比特流。

- 辅助工具:熟悉ModelSim/QuestaSim进行功能仿真,使用Synplify Pro进行逻辑综合,掌握MATLAB/Python进行算法建模与验证。

实践与项目经验

企业尤其看重候选人的动手能力,以下经验类型更具竞争力:

- 课程设计/竞赛:如数字逻辑课程设计(简易CPU、UART通信)、全国大学生电子设计竞赛、FPGA创新设计大赛等项目中承担的核心角色。

- 实验室项目:参与导师的科研项目,如图像处理加速(边缘检测、目标识别)、通信系统(OFDM调制解调)、电机控制等方向的FPGA实现。

- 实习经历:在通信设备商(华为、中兴)、半导体公司(AMD、Intel)或AI硬件企业(寒武纪、地平线)实习期间,参与过完整的FPGA开发流程(需求分析→设计→验证→测试)。

软技能与职业素养

- 问题解决能力:面对时序违例、功能bug时,能通过逻辑分析仪、SignalTap等工具定位问题并优化方案。

- 团队协作能力:能与软件工程师、硬件工程师协同工作,理解跨模块接口需求(如与ARM处理器的通信协议)。

- 学习能力:FPGA技术迭代快(如异构计算、OpenCL加速),需持续学习新器件特性与开发方法。

求职准备策略

简历优化

- 突出核心技能:在技能栏明确列出掌握的HDL语言、开发工具、项目工具链,熟练使用Verilog+Vivado完成图像边缘检测算法加速,时序满足200MHz要求”。

- 量化项目成果:用数据体现项目价值,如“优化FIR滤波器资源占用,减少BRAM使用40%,提升处理速度30%”。

- 针对性调整:投递通信类企业时,强调5G基带处理、LDPC编解码经验;投递AI企业时,突出神经网络加速、量化部署项目。

面试准备

- 技术笔试:常见考点包括HDL代码改错(如阻塞/非阻塞赋值错误)、时序分析(建立时间/保持时间)、电路设计(同步/异步电路区别)、FPGA架构(BRAM与分布式RAM区别),建议通过《FPGA之道》《Verilog数字系统设计教程》等教材巩固基础,刷牛客网、LeetCode相关题库。

- 项目深挖:准备STAR法则(情境-任务-行动-结果)描述项目,重点说明“遇到的技术难点及解决思路”,在DDR数据读写中,通过双缓冲机制解决数据竞争问题,确保传输稳定性”。

- 企业认知:了解目标公司的核心业务(如华为海思聚焦ASIC/FPGA设计,Xilinx主打数据中心加速),熟悉其FPGA产品线(如Xilinx Kintex/Artix系列),面试时体现对企业的关注。

资源渠道

- 校招信息:关注企业官网“校园招聘”板块、高校就业信息网、半导体行业公众号(如“FPGA开发圈”“芯片之家”)。

- 内推机会:通过导师、学长学姐或LinkedIn联系企业工程师,内推可提高简历筛选通过率。

- 社群交流:加入FPGA技术交流群(如QQ群“FPGA学习与求职”),获取面经、笔试资料及行业动态。

面试流程与常见问题

以头部企业为例,FPGA工程师校招通常包含以下环节:

| 环节 | 内容说明 |

|---|---|

| 简历筛选 | 重点看项目经验、技能匹配度(如要求“熟悉PCIe协议”,则相关项目经历优先) |

| 笔试 | 选择题(数字电路、计算机组成)+ 编程题(Verilog实现逻辑功能)+ 简答题(时序分析) |

| 技术一面 | 基础知识深挖(如“解释FPGA与CPLD的区别”“跨时钟域处理方法”) |

| 技术二面 | 项目经验复盘+场景题(如“如何优化一个高速数据采集系统的资源占用”) |

| HR面 | 职业规划、团队合作、抗压能力等软技能考察 |

常见技术问题示例:

-

“用Verilog实现一个带同步复位的16位计数器,要求复位信号高电平有效,计数到65539时归零。”

核心考察点:同步复位设计(避免亚稳态)、计数器溢出处理,参考代码:module counter16( input clk, input rst_n, output reg [15:0] cnt ); always @(posedge clk) begin if (!rst_n) cnt <= 16'd0; else if (cnt == 16'd65539) cnt <= 16'd0; else cnt <= cnt + 1; end endmodule -

“FPGA设计中,如何进行跨时钟域数据传输?有哪些注意事项?”

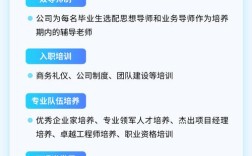

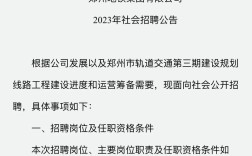

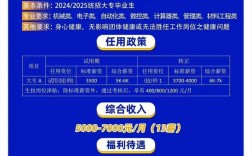

答案要点:常用方法包括握手协议、FIFO(异步FIFO需处理满/空标志位)、格雷码(避免亚稳态);注意事项包括同步器打拍、建立/保持时间检查、避免组合逻辑环路。 (图片来源网络,侵删)

(图片来源网络,侵删)

职业发展路径

FPGA工程师的职业发展呈现“技术深耕”与“管理转型”双通道:

- 技术专家路线:初级工程师→高级工程师→主任工程师→系统架构师,聚焦FPGA底层设计、性能优化或特定领域(如AI加速、通信协议)的技术突破。

- 管理路线:工程师→项目组长→技术经理→部门总监,需积累团队管理、项目规划、跨部门协作经验。

- 横向拓展:可转向ASIC设计验证、嵌入式系统开发、算法工程师(硬件加速方向),或进入FPGA工具链开发(如EDA工具)。

行业资深人士建议,应届生入职后前3年应夯实基础,参与至少2个完整项目,熟悉从需求到量产的全流程;3-5年可选择细分领域深耕(如高速接口、低功耗设计),考取相关专业认证(如Xilinx ACE认证)提升竞争力。

相关问答FAQs

Q1:非科班(如计算机、自动化专业)学生,如何转行成为FPGA工程师?

A:非科班学生需补足数字电路、HDL语言等核心知识,建议通过以下路径:①系统学习《数字逻辑设计》《Verilog HDL程序设计》等课程;②从简单项目入手(如LED流水灯、按键消抖),逐步过渡到复杂设计(如UART通信、I2C控制器);③参与开源项目(如GitHub上的FPGA学习工程)或在线课程(如Coursera“FPGA开发实战”),积累项目经验;④实习时优先选择FPGA相关岗位,即使从基础验证工作做起,也能快速熟悉开发流程。

Q2:FPGA工程师与IC设计工程师的区别是什么?求职时如何选择?

A:核心区别在于设计对象与灵活性:FPGA工程师基于现成FPGA芯片进行二次开发,侧重逻辑实现与优化,开发周期短、可灵活重构;IC设计工程师负责ASIC芯片的全流程设计(前端设计/后端布局/流片),涉及底层电路设计与半导体工艺,开发周期长、成本高但性能更优,求职选择时:若喜欢快速迭代、跨领域应用(如通信/AI/工业控制),可选FPGA;若对底层电路、半导体工艺感兴趣,能承受较长学习周期,可选IC设计,目前FPGA岗位需求更广,入门门槛相对较低,适合应届生积累实战经验。